# IA-32 インテル® アーキテクチャソフトウェア・デベロッパーズ・マニュアル

中巻 B:

命令セット・リファレンス N-Z

### 注記:

『IA-32 インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル』は、次の4巻から構成されています。

上巻:基本アーキテクチャ (資料番号 253665-013J) 中巻 A:命令セット・リファレンス A-M (資料番号 253666-013J) 中巻 B:命令セット・リファレンス N-Z (資料番号 253667-013J) 下巻:システム・プログラミング・ガイド (資料番号 253668-013J)

設計する際は、これら4巻すべてを参照してください。

2004年

## 【輸出規制に関する告知と注意事項】

本資料に掲載されている製品のうち、外国為替および外国為替管理法に定める戦略物資等または役務に該当するものについては、輸出または再輸出する場合、同法に基づく日本政府の輸出許可が必要です。また、米国産品である当社製品は日本からの輸出または再輸出に際し、原則として米国政府の事前許可が必要です。

### 【資料内容に関する注意事項】

- ・本ドキュメントの内容を予告なしに変更することがあります。

- ・ インテルでは、この資料に掲載された内容について、市販製品に使用した場合の保証あるいは特別な目的に合うことの保証等は、いかなる場合についてもいたしかねます。また、このドキュメント内の誤りについても責任を負いかねる場合があります。

- インテルでは、インテル製品の内部回路以外の使用にて責任を負いません。また、外部回路の特許についても関知いたしません。

- ・本書の情報はインテル製品を使用できるようにする目的でのみ記載されています。インテルは、製品について「取引条件」で提示されている場合を除き、インテル製品の販売や使用に関して、いかなる特許または著作権の侵害をも含み、あらゆる責任を負わないものとします。

- ・ いかなる形および方法によっても、インテルの文書による許可なく、この資料の一部またはすべてを複写することは禁じられています。

IA-32 アーキテクチャ・プロセッサ(インテル® Pentium® 4 プロセッサ、インテル® Pentium® III プロセッサなど)、エラッタと呼ばれる設計上の不具合が含まれている可能性があり、公表されている仕様とは異なる動作をする場合があります。現在確認済みのエラッタについては、インテルまでお問い合わせください。

ハイパー・スレッディング・テクノロジを利用するには、ハイパー・スレッディング・テクノロジに対応したインテル Pentium 4 プロセッサを搭載したコンピュータ・システム、および同技術に対応したチップセットと BIOS、OS が必要です。性能は、使用するハードウェアやソフトウェアによって異なります。HT テクノロジに対応したプロセッサの情報等、詳細については http://www.intel.co.jp/jp/info/hyperthreading/を参照してください。

インテル、Intel ロゴ、Intel386、Intel486、Intel NetBurst、Celeron、MMX、Pentium、Xeon は、アメリカ合衆国およびその他の国における Intel Corporation またはその子会社の商標、登録商標です。

- \* その他の社名、製品名などは、一般に各社の商標または登録商標です。

- © 1997-2004, Intel Corporation.

# 命令セット・ リファレンス N-Z

第4章では、第3章に続き、IA-32命令 (N-Z) についてアルファベット順に説明する。IA-32命令の前半部分 (A-M) については『IA-32インテル®アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、中巻 A』を参照のこと。

# **NEG—Two's Complement Negation**

| オペコード | 命令        | 説明                            |

|-------|-----------|-------------------------------|

| F6 /3 | NEG r/m8  | 2 の補数が r/m8 をネゲートする。          |

| F7 /3 | NEG r/m16 | 2 の補数が <i>r/m16</i> をネゲートする。  |

| F7 /3 | NEG r/m32 | 2 の補数が <i>r/m</i> 32 をネゲートする。 |

## 説明

オペランド (デスティネーション・オペランド) の値をその2の補数で置き換える。 (この操作は、オペランドの0からの減算と同等である。) デスティネーション・オペランドは、汎用レジスタまたはメモリ・ロケーションである。

この命令をLOCKプリフィックスと共に使用すると、アトミックに命令を実行させることができる。

# 操作

```

IF DEST = 0

THEN CF \leftarrow 0

ELSE CF \leftarrow 1;

FI;

DEST \leftarrow - (DEST)

```

# 影響を受けるフラグ

ソース・オペランドが0である場合は、CFフラグが0にセットされる。そうでない場合は、CFフラグが1にセットされる。OF、SF、ZF、AF、PFフラグが結果にしたがってセットされる。

# NEG—Two's Complement Negation (続き)

## 保護モード例外

#GP(0) デスティネーションが書き込み不可能なセグメントにある場合。

メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

DS、ES、FS、または GS レジスタの内容がヌル・セグメント・セレ

クタの場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) 現行特権レベルが3のときに、アライメント・チェックがイネーブル

にされていて、アライメントが合わないメモリ参照が行われた場合。

## 実アドレスモード例外

#GP メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

#SS メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

# 仮想 8086 モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) アライメント・チェックがイネーブルにされていて、アライメントが

合わないメモリ参照が行われた場合。

# **NOP—No Operation**

| オペコード | 命令  | 説明   |

|-------|-----|------|

| 90    | NOP | 操作なし |

# 説明

何の操作も実行されない。この命令は、命令ストリーム内で空間を占めるが、EIP レジスタを除いて、マシン・コンテキストに影響を与えない1バイト命令である。

NOP命令は、XCHG(E)AX、(E)AX命令の別名ニーモニックである。

# 影響を受けるフラグ

なし。

# 例外(すべての操作モード)

なし。

# **NOT—One's Complement Negation**

| オペコード | 命令        | 説明                |

|-------|-----------|-------------------|

| F6 /2 | NOT r/m8  | r/m8 の各ビットを反転する。  |

| F7 /2 | NOT r/m16 | r/m16 の各ビットを反転する。 |

| F7 /2 | NOT r/m32 | r/m32 の各ビットを反転する。 |

# 説明

デスティネーション・オペランドにビット単位のNOT(否定)演算(各1が0にセットされ、各0が1にセットされる)を実行し、結果をデスティネーション・オペランド・ロケーションにストアする。デスティネーション・オペランドには、レジスタまたはメモリ・ロケーションを使用できる。

この命令をLOCKプリフィックスと共に使用すると、アトミックに命令を実行させることができる。

# 操作

DEST ← NOT DEST;

# 影響を受けるフラグ

なし。

# 保護モード例外

#GP(0) デスティネーション・オペランドが書き込み不可能なセグメントを指

している場合。

メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

DS、ES、FS、または GS レジスタの内容がヌル・セグメント・セレ

クタの場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#**PF** (フォルトコード) ページフォルトが発生した場合。

#AC(0) 現行特権レベルが3のときに、アライメント・チェックがイネーブル

にされていて、アライメントが合わないメモリ参照が行われた場合。

# 実アドレスモード例外

#GP メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

#SS メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

# NOT—One's Complement Negation (続き)

# 仮想 8086 モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) アライメント・チェックがイネーブルにされていて、アライメントが

合わないメモリ参照が行われた場合。

# OR—Logical Inclusive OR

| オペコード           | 命令                            | 説明                           |

|-----------------|-------------------------------|------------------------------|

| 0C ib           | OR AL, imm8                   | AL と <i>imm8</i> との OR をとる。  |

| 0D <i>iw</i>    | OR AX, imm16                  | AX と imm16 との OR をとる。        |

| 0D id           | OR EAX, imm32                 | EAX と imm32 との OR をとる。       |

| 80 /1 <i>ib</i> | OR r/m8, imm8                 | r/m8 と imm8 との OR をとる。       |

| 81 /1 <i>iw</i> | OR r/m16, imm16               | r/m16と imm16との OR をとる。       |

| 81 /1 <i>id</i> | OR r/m32, imm32               | r/m32 と imm32 との OR をとる。     |

| 83 /1 <i>ib</i> | OR <i>r/m16</i> , <i>imm8</i> | r/m16 と imm8(符号拡張)との OR をとる。 |

| 83 /1 <i>ib</i> | OR r/m32, imm8                | r/m32 と imm8(符号拡張)との OR をとる。 |

| 08 /r           | OR <i>r/m8</i> , <i>r8</i>    | r/m8 と r8 との OR をとる。         |

| 09 /r           | OR <i>r/m16</i> , <i>r16</i>  | r/m16 と r16 との OR をとる。       |

| 09 /r           | OR <i>r/m32</i> , <i>r32</i>  | r/m32 と r32 との OR をとる。       |

| 0A /r           | OR r8, r/m8                   | r8 と r/m8 との OR をとる。         |

| 0B /r           | OR r16, r/m16                 | r16 と r/m16 との OR をとる。       |

| 0B /r           | OR r32, r/m32                 | r32 と r/m32 との OR をとる。       |

# 説明

デスティネーション・オペランド(第1オペランド)とソース・オペランド(第2オペランド)との間のビット単位のOR(論理和)演算を実行し、結果をデスティネーション・オペランド・ロケーションにストアする。ソース・オペランドには、即値、レジスタ、またはメモリ・ロケーションを使用できる。デスティネーション・オペランドには、レジスタまたはメモリ・ロケーションを使用できる。(ただし、1つの命令に2つのメモリ・オペランドを使用することはできない。)OR命令の各ビットの結果は、第1オペランドと第2オペランドの対応するビットが両方とも0である場合は0にセットされ、そうでない場合は1にセットされる。

この命令をLOCKプリフィックスと共に使用すると、アトミックに命令を実行させることができる。

# 操作

DEST ← DEST OR SRC;

## 影響を受けるフラグ

OF および CF フラグがクリアされ、SF、ZF、PF フラグが結果にしたがってセットされる。AF フラグの状態は未定義。

# OR-Logical Inclusive OR (続き)

## 保護モード例外

#GP(0) デスティネーション・オペランドが書き込み不可能なセグメントを指

している場合。

メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

DS、ES、FS、または GS レジスタの内容がヌル・セグメント・セレ

クタの場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) 現行特権レベルが3のときに、アライメント・チェックがイネーブル

にされていて、アライメントが合わないメモリ参照が行われた場合。

# 実アドレスモード例外

#GP メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

#SS メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

# 仮想 8086 モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) アライメント・チェックがイネーブルにされていて、アライメントが

合わないメモリ参照が行われた場合。

# ORPD—Bitwise Logical OR of Packed Double-Precision Floating-Point Values

オペコード 命令 説明

66 0F 56 /r ORPD xmm1, xmm2/m128 xmm2/m128 と xmm1 のビット単位の OR (論理和)

演算を実行する。

### 説明

ソース・オペランド (第2オペランド) の2つのパックド倍精度浮動小数点値とデス ティネーション・オペランド(第1オペランド)の2つのパックド倍精度浮動小数点 値の間でビット単位の OR (論理和) 演算を実行し、結果をデスティネーション・オ ペランドに格納する。ソース・オペランドは、XMM レジスタまたは 128 ビットのメ モリ・ロケーションである。デスティネーション・オペランドはXMM レジスタである。

# 操作

DEST[127-0]  $\leftarrow$  DEST[127-0] BitwiseOR SRC[127-0];

## 同等のインテル® C/C++ コンパイラ組み込み関数

ORPD \_\_m128d \_mm\_or\_pd(\_\_m128d a, \_\_m128d b)

## SIMD 浮動小数点例外

なし。

### 保護モード例外

CS、DS、ES、FS、またはGS セグメント内のメモリ・オペランドの #GP(0)

実効アドレスが無効の場合。

セグメントに関係なく、メモリ・オペランドのアライメントが 16 バ

イトに合っていない場合。

SSセグメント内のアドレスが無効の場合。 #SS(0)

#PF (フォルトコード) ページフォルトが発生した場合。

CR0 の TS がセットされた場合。 #NM CR0のEMがセットされた場合。 #UD

CR4のOSFXSRが0の場合。

CPUID 機能フラグ SSE2 が 0 の場合。

# ORPD—Bitwise Logical OR of Packed Double-Precision Floating-Point Values(続き)

# 実アドレスモード例外

#GP(0) セグメントに関係なく、メモリ・オペランドのアライメントが 16 バ

イトに合っていない場合。

オペランドの一部が0~FFFFHの実効アドレス空間の範囲外の場合。

#NM CR0 の TS がセットされた場合。 #UD CR0 の EM がセットされた場合。

CR4のOSFXSRが0の場合。

CPUID 機能フラグ SSE2 が 0 の場合。

# 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

# **ORPS—Bitwise Logical OR of Packed Single-Precision Floating-Point Values**

OF 56 /r ORPS xmm1, xmm2/m128 xmm2/m128 と xmm1 のビット単位の OR (論理和)

演算を実行する。

### 説明

ソース・オペランド(第2オペランド)の4つのパックド単精度浮動小数点値とデスティネーション・オペランド(第1オペランド)の4つのパックド単精度浮動小数点値の間でビット単位のOR(論理和)演算を実行し、結果をデスティネーション・オペランドに格納する。ソース・オペランドは、XMM レジスタまたは128 ビットのメモリ・ロケーションである。デスティネーション・オペランドはXMM レジスタである。

# 操作

DEST[127-0]  $\leftarrow$  DEST[127-0] BitwiseOR SRC[127-0];

同等のインテル® C/C++ コンパイラ組み込み関数

ORPS \_\_m128 \_mm\_or\_ps(\_\_m128 a, \_\_m128 b)

SIMD 浮動小数点例外

なし。

### 保護モード例外

#GP(0) CS、DS、ES、FS、またはGS セグメント内のメモリ・オペランドの

実効アドレスが無効の場合。

セグメントに関係なく、メモリ・オペランドのアライメントが 16 バ

イトに合っていない場合。

#SS(0) SS セグメント内のアドレスが無効の場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#NM CR0 の TS がセットされた場合。 #UD CR0 の EM がセットされた場合。

CR4のOSFXSRが0の場合。

CPUID 機能フラグ SSE が 0 の場合。

# ORPS—Bitwise Logical OR of Packed Single-Precision Floating-Point Values (続き)

# 実アドレスモード例外

#GP(0) セグメントに関係なく、メモリ・オペランドのアライメントが 16 バ

イトに合っていない場合。

オペランドの一部が0~FFFFHの実効アドレス空間の範囲外の場合。

#NM CR0 の TS がセットされた場合。 #UD CR0 の EM がセットされた場合。

CR4のOSFXSRが0の場合。

CPUID 機能フラグ SSE が 0 の場合。

# 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

# **OUT—Output to Port**

| オペコード | 命令            | 説明                                     |

|-------|---------------|----------------------------------------|

| E6 ib | OUT imm8, AL  | AL にあるバイトを I/O ポートアドレス imm8 に出力する。     |

| E7 ib | OUT imm8, AX  | AX にあるワードを I/O ポートアドレス imm8 に出力する。     |

| E7 ib | OUT imm8, EAX | EAX にあるダブルワードを I/O ポートアドレス imm8 に出力する。 |

| EE    | OUT DX, AL    | AL にあるバイトを DX にある I/O ポートアドレスに出力する。    |

| EF    | OUT DX, AX    | AX にあるワードを DX にある I/O ポートアドレスに出力する。    |

| EF    | OUT DX, EAX   | EAXにあるダブルワードをDXにあるI/Oポートアドレスに出力する。     |

### 説明

値を第2オペランド (ソース・オペランド) からデスティネーション・オペランド (第1オペランド) で指定された I/O ポートにコピーする。ソース・オペランドには、アクセスされるポートのサイズ (8、16、または 32 ビット) に応じてそれぞれ AL、AX、または EAX レジスタを使用できる。デスティネーション・オペランドには、バイト即値または DX レジスタを使用できる。バイト即値を使用すると、I/O ポートアドレス 0 ~ 255 をアクセスすることができる。ソース・オペランドとして DX レジスタを使用すると、I/O ポート 0 ~ 65.535 をアクセスすることができる。

アクセスされる I/O ポートのサイズは、8 ビットの I/O ポートではオペコードによって決まり、16 ビットまたは 32 ビットの I/O ポートでは命令のオペランド・サイズ属性によって決まる。

マシン・コード・レベルでは、I/O 命令は、8 ビットの I/O ポートをアクセスするとき は短くなる。この場合は、ポートアドレスの上位8 ビットは0 になる。

この命令は、プロセッサの I/O アドレス空間にある I/O ポートのアクセスだけに有用である。 I/O アドレス空間にある I/O ポートのアクセスに関する詳細については、『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、上巻』の第13章「入出力」を参照のこと。

### IA-32 アーキテクチャにおける互換性

OUT 命令を実行した後、インテル® Pentium®プロセッサは、次の命令の実行を開始する前に、EWBE# ピンがアクティブにサンプリングされていることを保証する。(EWBE# がアクティブでない場合でも命令をプリフェッチすることはできるが、EWBE# ピンがアクティブにサンプリングされるまで命令は実行されないことに注意すること。) インテル Pentium プロセッサ・ファミリだけに EWBE# ピンがあり、他のIA-32 プロセッサにはない。

# OUT—Output to Port(続き)

# 操作

```

IF ((PE = 1) AND ((CPL > IOPL) OR (VM = 1)))

THEN (* Protected mode with CPL > IOPL or virtual-8086 mode *)

IF (Any I/O Permission Bit for I/O port being accessed = 1)

THEN (* I/O operation is not allowed *)

#GP(0);

ELSE (* I/O operation is allowed *)

DEST ← SRC; (* Writes to selected I/O port *)

FI;

ELSE (Real Mode or Protected Mode with CPL ≤ IOPL *)

DEST ← SRC; (* Writes to selected I/O port *)

FI;

```

# 影響を受けるフラグ

なし。

# 保護モード例外

#GP(0)

CPL が I/O 特権レベル(IOPL)より大きく(低い特権をもつ)、アクセスされる I/O ポートの TSS にある対応する I/O パーミッション・ビットのいずれかが 1 である場合。

## 実アドレスモード例外

なし。

### 仮想 8086 モード例外

#GP(0)

アクセスされる I/O ポートの TSS にある対応する I/O パーミッション・ビットのいずれかが 1 である場合。

# OUTS/OUTSB/OUTSW/OUTSD—Output String to Port

| オペコード | 命令           | 説明                                                              |

|-------|--------------|-----------------------------------------------------------------|

| 6E    | OUTS DX, m8  | バイトを DS:(E)SI に指定されたメモリ・ロケーションから DX に指定された I/O ポートに出力する。        |

| 6F    | OUTS DX, m16 | ワードを DS:(E)SI に指定されたメモリ・ロケーションから DX に指定された I/O ポートに出力する。        |

| 6F    | OUTS DX, m32 | ダブルワードを DS:(E)SI に指定されたメモリ・ロケーションから DX に指定された I/O ポートに出力する。     |

| 6E    | OUTSB        | バイトを DS:(E)SI に指定されたメモリ・ロケーションから DX に指定された I/O ポートに出力する。        |

| 6F    | OUTSW        | ワードを DS:(E)SI に指定されたメモリ・ロケーションから DX に指定された I/O ポートに出力する。        |

| 6F    | OUTSD        | ダブルワードを DS:(E)SI に指定されたメモリ・ロケー<br>ションから DX に指定された I/O ポートに出力する。 |

# 説明

データをソース・オペランド (第2オペランド) からデスティネーション・オペランド (第1オペランド) で指定された I/O ポートにコピーする。ソース・オペランドはメモリ・ロケーションであり、そのアドレスは、(命令のアドレスサイズ属性、32または 16 に応じて) それぞれ DS: EDI レジスタまたは DS: DI レジスタから読み取られる。DS セグメントをセグメント・オーバライド・プリフィックスでオーバライドすることができる。デスティネーション・オペランドは、DX レジスタから読み取られる I/O ポートアドレス ( $0\sim65,535$ ) である。アクセスされる I/O ポートのサイズ (すなわち、ソース・オペランドとデスティネーション・オペランドのサイズ) は、8 ビットの I/O ポートではオペコードによって決まり、16 ビットまたは 32 ビットの I/O ポートでは命令のオペランド・サイズ属性によって決まる。

アセンブリ・コード・レベルでは、この命令の「明示オペランド」形式と「オペランドなし」形式という2つの形式が使用できる。(OUTSニーモニックで指定される)明示オペランド形式では、ソース・オペランドとデスティネーション・オペランドを明示的に指定できる。この場合、ソース・オペランドは、I/Oポートのサイズとソースアドレスを示す記号でなければならない。デスティネーション・オペランドは、DXでなければならない。この明示オペランド形式は、ドキュメンテーションを可能にするために設けられたものであるが、この形式によって提供されるドキュメンテーションは誤解を招く場合があるので注意する。すなわち、ソース・オペランドの記号は、オペランドの正しいタイプ(サイズ:バイト、ワード、またはダブルワード)を指定しなければならないが、正しいロケーションを指定する必要はない。ロケーションは、常にDS:(E)SIレジスタによって指定されるので、OUTS命令を実行する前に、このレジスタに正しくロードされていなければならない。

# OUTS/OUTSB/OUTSW/OUTSD—Output String to Port(続き)

オペランドなし形式は、OUTS 命令のバイト、ワード、ダブルワード各バージョンの「ショート形式」を提供する。この場合も、DS:(E)SI がソース・オペランドであると想定され、DX がデスティネーション・オペランドであると想定される。I/O ポートのサイズは、OUTSB(バイト)、OUTSW(ワード)、またはOUTSD(ダブルワード)の各ニーモニックの選択で指定される。

バイト、ワード、またはダブルワードがメモリ・ロケーションから I/O ポートに転送された後、(E)SI レジスタは EFLAGS レジスタ内の DF フラグの設定にしたがって自動的にインクリメントまたはデクリメントされる(DF フラグが 0 である場合は、(E)SI レジスタはインクリメントされる。DF フラグが 1 である場合は、(E)SI レジスタはデクリメントされる)。(E)SI レジスタは、バイト操作の場合は 1、ワード操作の場合は 2、ダブルワード操作の場合は 4、それぞれインクリメントまたはデクリメントされる。

OUTS、OUTSB、OUTSW、OUTSD命令は、前にREPプリフィックスを付けることにより、ECX バイト、ワード、またはダブルワードのブロック入力を行うことができる。REPプリフィックスの説明については、本章の「REP/REPE/REPZ/REPNE/REPNZ—Repeat String Operation Prefix」を参照のこと。

この命令は、プロセッサの I/O アドレス空間にある I/O ポートのアクセスだけに有用である。 I/O アドレス空間にある I/O ポートへのアクセスに関する詳細については、『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、上巻』の第13章「入出力」を参照のこと。

# IA-32 アーキテクチャにおける互換性

OUTS、OUTSB、OUTSW、またはOUTSD命令を実行した後、インテル® Pentium®プロセッサは、次の命令の実行を開始する前に、EWBE# ピンがアクティブにサンプリングされていることを保証する。(EWBE# がアクティブでない場合でも命令をプリフェッチすることはできるが、EWBE# ピンがアクティブにサンプリングされるまで命令は実行されないことに注意すること。)インテル Pentium プロセッサ・ファミリだけに EWBE# ピンがあり、他の IA-32 プロセッサにはない。インテル® Pentium® 4 プロセッサ、インテル® Xeon™ プロセッサ、および P6 ファミリのプロセッサは、OUTS、OUTSB、OUTSW、または OUTSD 命令の実行時に、そのトランザクションのデータフェーズが完了してから次の命令を実行する。

# OUTS/OUTSB/OUTSW/OUTSD—Output String to Port (続き)

# 操作

```

IF ((PE = 1) AND ((CPL > IOPL) OR (VM = 1)))

THEN (* Protected mode with CPL > IOPL or virtual-8086 mode *)

IF (Any I/O Permission Bit for I/O port being accessed = 1)

THEN (* I/O operation is not allowed *)

#GP(0):

ELSE ( * I/O operation is allowed *)

DEST ← SRC; (* Writes to I/O port *)

FI:

ELSE (Real Mode or Protected Mode with CPL ≤ IOPL *)

DEST ← SRC; (* Writes to I/O port *)

FI;

IF (byte transfer)

THEN IF DF = 0

THEN (E)SI \leftarrow (E)SI + 1;

ELSE (E)SI \leftarrow (E)SI - 1;

FI;

ELSE IF (word transfer)

THEN IF DF = 0

THEN (E)SI \leftarrow (E)SI + 2;

ELSE (E)SI \leftarrow (E)SI -2;

FI:

ELSE (* doubleword transfer *)

THEN IF DF = 0

THEN (E)SI \leftarrow (E)SI + 4;

ELSE (E)SI \leftarrow (E)SI - 4;

FI:

FI;

FI;

```

# 影響を受けるフラグ

なし。

# 保護モード例外

#GP(0) CPL が I/O 特権レベル (IOPL) より大きく (低い特権をもつ)、アクセスされる I/O ポートの TSS にある対応する I/O パーミッション・ビットのいずれかが 1 である場合。

メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GSセグメントの範囲外の場合。

セグメント・レジスタの内容がヌル・セグメント・セレクタの場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) 現行特権レベルが 3 のときに、アライメント・チェックがイネーブルにされていて、アライメントが合わないメモリ参照が行われた場合。

# OUTS/OUTSB/OUTSW/OUTSD—Output String to Port (続き)

# 実アドレスモード例外

#GP メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

#SS メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

# 仮想 8086 モード例外

#GP(0) アクセスされる I/O ポートの TSS にある対応する I/O パーミッショ

ン・ビットのいずれかが1である場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) アライメント・チェックがイネーブルにされていて、アライメントが

合わないメモリ参照が行われた場合。

# PACKSSWB/PACKSSDW—Pack with Signed Saturation

| オペコード       | 命令                          | 説明                                                                                                |

|-------------|-----------------------------|---------------------------------------------------------------------------------------------------|

| 0F 63 /r    | PACKSSWB mm1,<br>mm2/m64    | 符号付き飽和処理を使用して、 <i>mm1 と mm2/m64 の</i> 4 個のパックド符号付きワード整数を、 <i>mm1</i> の 8 個のパックド符号付きバイト整数に変換する。    |

| 66 0F 63 /r | PACKSSWB xmm1,<br>xmm2/m128 | 符号付き飽和処理を使用して、xmm1 と xmm2/m128 の 8 個のパックド符号付きワード整数を、xmm1 の 16 個のパックド符号付きバイト整数に変換する。               |

| 0F 6B /r    | PACKSSDW mm1,<br>mm2/m64    | 符号付き飽和処理を使用して、 <i>mm1 と mm2/m64 の</i> 2 個のパックド符号付きダブルワード整数を、 <i>mm1</i> の 4 個のパックド符号付きワード整数に変換する。 |

| 66 0F 6B /r | PACKSSDW xmm1,<br>xmm2/m128 | 符号付き飽和処理を使用して、xmm1と xmm2/m128の4個のパックド符号付きダブルワード整数を、xmm1の8個のパックド符号付きワード整数に変換する。                    |

# 説明

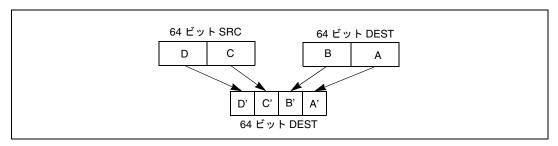

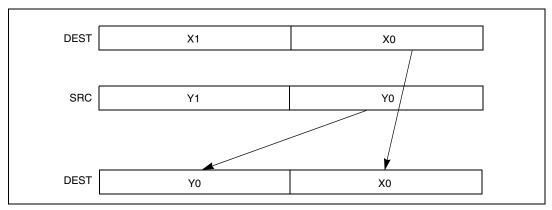

オーバーフロー条件を処理する飽和処理を使用して、パックド符号付きワード整数をパックド符号付きバイト整数に変換する(PACKSSWB の場合)か、あるいはパックド符号付きダブルワード整数をパックド符号付きワード整数に変換する(PACKSSDWの場合)。パック操作の例については、図4-1.を参照のこと。

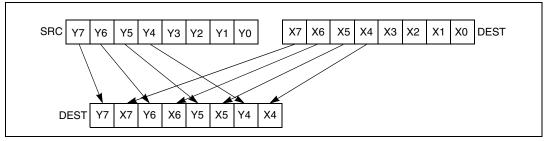

図 4-1. 64 ビット・オペランドを使用しての PACKSSDW 命令の操作

PACKSSWB 命令は、デスティネーション・オペランド(第1オペランド)の4個または8個の符号付きワード整数とソース・オペランド(第2オペランド)の4個または8個の符号付きワード整数を、8個または16個の符号付きバイト整数に変換し、デスティネーション・オペランドにその結果をストアする。符号付きワード整数値が符号付きバイト整数の範囲を超える場合(すなわち、正の整数では7FHより大きく、負の整数では80Hより大きい場合)は、飽和された符号付きバイト整数値である7FHまたは80Hがデスティネーションにストアされる。

# PACKSSWB/PACKSSDW—Pack with Signed Saturation (続き)

PACKSSDW命令は、デスティネーション・オペランド(第1オペランド)の2個または4個の符号付きダブルワードとソース・オペランド(第2オペランド)の2個または4個の符号付きダブルワードを、デスティネーション・オペランドの4個または8個の符号付きワードにパックする(図4-1.を参照)。符号付きダブルワード整数値が符号付きワードの範囲を超える場合(すなわち、正の整数では7FFFHより大きく、負の整数では8000Hより大きい場合)は、飽和された符号付きワード整数値である7FFFHまたは8000Hがデスティネーションにストアされる。

PACKSSWB 命令および PACKSSDW 命令は、64 ビット・オペランドまたは 128 ビット・オペランドのいずれかを操作する。64 ビット・オペランドを操作する場合、デスティネーション・オペランドには MMX®テクノロジ・レジスタを使用しなければならないが、ソース・オペランドには MMX テクノロジ・レジスタまたは 64 ビット・メモリ・ロケーションのどちらを使用しても構わない。128 ビット・オペランドを操作する場合は、デスティネーション・オペランドには XMM レジスタを使用しなければならないが、ソース・オペランドには XMM レジスタまたは 128 ビット・メモリ・ロケーションのどちらを使用しても構わない。

## 操作

```

PACKSSWB instruction with 64-bit operands

```

DEST[7..0] ← SaturateSignedWordToSignedByte DEST[15..0];

DEST[15..8] ← SaturateSignedWordToSignedByte DEST[31..16];

DEST[23..16] ← SaturateSignedWordToSignedByte DEST[47..32];

DEST[31..24] ← SaturateSignedWordToSignedByte DEST[63..48];

DEST[39..32] ← SaturateSignedWordToSignedByte SRC[15..0];

DEST[47..40] ← SaturateSignedWordToSignedByte SRC[31..16];

DEST[55..48] ← SaturateSignedWordToSignedByte SRC[47..32]:

DEST[63..56] ← SaturateSignedWordToSignedByte SRC[63..48];

### PACKSSDW instruction with 64-bit operands

DEST[15..0] ← SaturateSignedDoublewordToSignedWord DEST[31..0]:

DEST[31..16] ← SaturateSignedDoublewordToSignedWord DEST[63..32];

DEST[47..32] ← SaturateSignedDoublewordToSignedWord SRC[31..0];

DEST[63..48] ← SaturateSignedDoublewordToSignedWord SRC[63..32];

# PACKSSWB instruction with 128-bit operands

DEST[7-0] ← SaturateSignedWordToSignedByte (DEST[15-0]);

DEST[15-8] ← SaturateSignedWordToSignedByte (DEST[31-16]);

DEST[23-16] ← SaturateSignedWordToSignedByte (DEST[47-32]);

DEST[31-24] ← SaturateSignedWordToSignedByte (DEST[63-48]);

DEST[39-32] ← SaturateSignedWordToSignedByte (DEST[79-64]);

DEST[47-40] ← SaturateSignedWordToSignedByte (DEST[95-80]);

DEST[55-48] ← SaturateSignedWordToSignedByte (DEST[111-96]);

DEST[63-56] ← SaturateSignedWordToSignedByte (DEST[127-112]);

DEST[71-64] ← SaturateSignedWordToSignedByte (SRC[15-0]);

DEST[79-72] ← SaturateSignedWordToSignedByte (SRC[31-16]);

# PACKSSWB/PACKSSDW—Pack with Signed Saturation (続き)

$$\begin{split} \mathsf{DEST}[87\text{-}80] \leftarrow \mathsf{SaturateSignedWordToSignedByte} \ (\mathsf{SRC}[47\text{-}32]); \\ \mathsf{DEST}[95\text{-}88] \leftarrow \mathsf{SaturateSignedWordToSignedByte} \ (\mathsf{SRC}[63\text{-}48]); \\ \mathsf{DEST}[103\text{-}96] \leftarrow \mathsf{SaturateSignedWordToSignedByte} \ (\mathsf{SRC}[79\text{-}64]); \\ \mathsf{DEST}[111\text{-}104] \leftarrow \mathsf{SaturateSignedWordToSignedByte} \ (\mathsf{SRC}[95\text{-}80]); \\ \mathsf{DEST}[119\text{-}112] \leftarrow \mathsf{SaturateSignedWordToSignedByte} \ (\mathsf{SRC}[111\text{-}96]); \\ \mathsf{DEST}[127\text{-}120] \leftarrow \mathsf{SaturateSignedWordToSignedByte} \ (\mathsf{SRC}[127\text{-}112]); \\ \end{split}$$

## PACKSSDW instruction with 128-bit operands

DEST[15-0]  $\leftarrow$  SaturateSignedDwordToSignedWord (DEST[31-0]); DEST[31-16]  $\leftarrow$  SaturateSignedDwordToSignedWord (DEST[63-32]); DEST[47-32]  $\leftarrow$  SaturateSignedDwordToSignedWord (DEST[95-64]); DEST[63-48]  $\leftarrow$  SaturateSignedDwordToSignedWord (DEST[127-96]); DEST[79-64]  $\leftarrow$  SaturateSignedDwordToSignedWord (SRC[31-0]); DEST[95-80]  $\leftarrow$  SaturateSignedDwordToSignedWord (SRC[63-32]); DEST[111-96]  $\leftarrow$  SaturateSignedDwordToSignedWord (SRC[95-64]); DEST[127-112]  $\leftarrow$  SaturateSignedDwordToSignedWord (SRC[127-96]);

# 同等のインテル® C/C++ コンパイラ組み込み関数

```

__m64 _mm_packs_pi16(__m64 m1, __m64 m2)

__m64 _mm_packs_pi32 (__m64 m1, __m64 m2)

```

# 影響を受けるフラグ

なし。

### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CR0 の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

# PACKSSWB/PACKSSDW—Pack with Signed Saturation (続き)

# 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合。

#UD CRO の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

#NM CR0 の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

# 仮想 8086 モード例外

実アドレスモード例外と同じ。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

# PACKUSWB—Pack with Unsigned Saturation

| オペコード       | 命令                          | 説明                                                                                   |

|-------------|-----------------------------|--------------------------------------------------------------------------------------|

| 0F 67 /r    | PACKUSWB mm,<br>mm/m64      | 符号なし飽和処理を使用して、mm の 4 個の符号付きワード整数と mm/m64 の 4 個の符号付きワード整数を、mm の 8 個の符号なしバイト整数に変換する。   |

| 66 0F 67 /r | PACKUSWB xmm1,<br>xmm2/m128 | 符号なし飽和処理を使用して、xmm1の8個の符号付きワード整数と xmm2/m128 の 8 個の符号付きワード整数を、xmm1の16個の符号なしバイト整数に変換する。 |

# 説明

デスティネーション・オペランド (第1オペランド) の4個または8個の符号付きワード整数とソース・オペランド (第2オペランド) の4個または8個の符号付きワード整数を、8個または16個の符号なしバイト整数に変換し、デスティネーション・オペランドにその結果をストアする (パック操作の例については、図4-1.を参照のこと)。符号付きワード整数値が符号なしバイト整数の範囲を超える場合 (すなわち、FFHより大きいか、00Hより小さい場合) は、飽和された符号なしバイト整数値である FFHまたは00Hがデスティネーションにストアされる。

PACKUSWB 命令は、64 ビット・オペランドまたは 128 ビット・オペランドのいずれかを操作する。64 ビット・オペランドを操作する場合、デスティネーション・オペランドには MMX®テクノロジ・レジスタを使用しなければならないが、ソース・オペランドには MMX テクノロジ・レジスタまたは 64 ビット・メモリ・ロケーションのどちらを使用しても構わない。128 ビット・オペランドを操作する場合は、デスティネーション・オペランドには XMM レジスタを使用しなければならないが、ソース・オペランドには XMM レジスタまたは 128 ビット・メモリ・ロケーションのどちらを使用しても構わない。

### 操作

PACKUSWB instruction with 64-bit operands:

DEST[7..0] ← SaturateSignedWordToUnsignedByte DEST[15..0]; DEST[15..8] ← SaturateSignedWordToUnsignedByte DEST[31..16];

$\mathsf{DEST}[23..16] \leftarrow SaturateSignedWordToUnsignedByte\ \mathsf{DEST}[47..32];$

${\sf DEST[31..24]} \leftarrow SaturateSignedWordToUnsignedByte\ DEST[63..48];$

DEST[39..32] ← SaturateSignedWordToUnsignedByte SRC[15..0]; DEST[47..40] ← SaturateSignedWordToUnsignedByte SRC[31..16];

DEST[55..48] ← SaturateSignedWordToUnsignedByte SRC[47..32];

DEST[63..56] ← SaturateSignedWordToUnsignedByte SRC[63..48];

## PACKUSWB instruction with 128-bit operands:

DEST[7-0] ← SaturateSignedWordToUnsignedByte (DEST[15-0]);

DEST[15-8] ← SaturateSignedWordToUnsignedByte (DEST[31-16]);

DEST[23-16] ← SaturateSignedWordToUnsignedByte (DEST[47-32]);

DEST[31-24] ← SaturateSignedWordToUnsignedByte (DEST[63-48]);

DEST[39-32] ← SaturateSignedWordToUnsignedByte (DEST[79-64]);

# PACKUSWB—Pack with Unsigned Saturation (続き)

$$\begin{split} \mathsf{DEST}[47\text{-}40] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{DEST}[95\text{-}80]); \\ \mathsf{DEST}[55\text{-}48] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{DEST}[111\text{-}96]); \\ \mathsf{DEST}[63\text{-}56] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{DEST}[127\text{-}112]); \\ \mathsf{DEST}[71\text{-}64] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{SRC}[15\text{-}0]); \\ \mathsf{DEST}[79\text{-}72] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{SRC}[31\text{-}16]); \\ \mathsf{DEST}[87\text{-}80] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{SRC}[47\text{-}32]); \\ \mathsf{DEST}[95\text{-}88] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{SRC}[63\text{-}48]); \\ \mathsf{DEST}[103\text{-}96] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{SRC}[79\text{-}64]); \\ \mathsf{DEST}[111\text{-}104] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{SRC}[95\text{-}80]); \\ \mathsf{DEST}[119\text{-}112] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{SRC}[111\text{-}96]); \\ \mathsf{DEST}[127\text{-}120] \leftarrow \mathsf{SaturateSignedWordToUnsignedByte} \; (\mathsf{SRC}[127\text{-}112]); \\ \mathsf{DEST}[127\text{-}120] \leftarrow \mathsf{SaturateSignedWordToUnsignedByt$$

# 同等のインテル® C/C++ コンパイラ組み込み関数

\_\_m64 \_mm\_packs\_pu16(\_\_m64 m1, \_\_m64 m2)

# 影響を受けるフラグ

なし。

## 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CR0 の EM がセットされた場合。

CR4の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

# PACKUSWB—Pack with Unsigned Saturation (続き)

# 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合

#UD CROのEMがセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ)上で128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

## 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

# PADDB/PADDW/PADDD—Add Packed Integers

| オペコード       | 命令                    | 説明                                         |

|-------------|-----------------------|--------------------------------------------|

| 0F FC /r    | PADDB mm, mm/m64      | <i>mm/m64</i> と <i>mm</i> のパックドバイト整数を加算する。 |

| 66 0F FC /r | PADDB xmm1, mm2/m128  | xmm2/m128と xmm1 のパックドバイト整数を加算<br>する。       |

| 0F FD /r    | PADDW mm, mm/m64      | <i>mm/m64</i> と <i>mm</i> のパックドワード整数を加算する。 |

| 66 0F FD /r | PADDW xmm1, xmm2/m128 | xmm2/m128と xmm1 のパックドワード整数を加算<br>する。       |

| 0F FE /r    | PADDD mm, mm/m64      | mm/m64 と mm のパックド・ダブルワード整数を<br>加算する。       |

| 66 0F FE /r | PADDD xmm1, xmm2/m128 | xmm2/m128 と xmm1 のパックド・ダブルワード整<br>数を加算する。  |

## 説明

ソース・オペランド(第2オペランド)とデスティネーション・オペランド(第1オペランド)のパックド整数のSIMD加算を実行し、結果のパックド整数をデスティネーション・オペランドに格納する。SIMD演算の図は、『IA-32 インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、上巻』の図 9-4. を参照のこと。以降の段落で説明するように、オーバーフローはラップアラウンドを使用して処理される。

上記の命令は、64 ビット・オペランドまたは128 ビット・オペランドのいずれかを操作する。64 ビット・オペランドを操作する場合、デスティネーション・オペランドにはMMX®テクノロジ・レジスタを使用しなければならないが、ソース・オペランドにはMMXテクノロジ・レジスタまたは64 ビット・メモリ・ロケーションのどちらを使用しても構わない。128 ビット・オペランドを操作する場合は、デスティネーション・オペランドには XMM レジスタを使用しなければならないが、ソース・オペランドには XMM レジスタまたは128 ビット・メモリ・ロケーションのどちらを使用しても構わない。

PADDB命令は、パックドバイト整数に加算する。個別の結果が8ビットで表現するには大きすぎるとき(オーバーフロー)、結果はラップアラウンドされ、下位8ビットがデスティネーション・オペランドに書き込まれる。

PADDW 命令は、パックドワード整数に加算する。個別の結果が 16 ビットで表現する には大きすぎるとき (オーバーフロー)、結果はラップアラウンドされ、下位 16 ビットがデスティネーション・オペランドに書き込まれる。

PADDD 命令は、パックド・ダブルワード整数を加算する。個別の結果が32 ビットで表現するには大きすぎるとき(オーバーフロー)、結果はラップアラウンドされ、下位32 ビットがデスティネーション・オペランドに書き込まれる。

# PADDB/PADDW/PADDD—Add Packed Integers (続き)

PADDB、PADDW、PADDD命令は、符号なしまたは符号付き(2の補数表記)のパックド整数を操作できることに注意すること。ただし、これらの命令は、オーバーフローやキャリーを示す EFLAGS レジスタ内のビットをセットしない。このため、検出されないオーバーフロー状態が発生しないように、操作される値の範囲をソフトウェアによって制御しなければならない。

# 操作

```

PADDB instruction with 64-bit operands:

DEST[7..0] \leftarrow DEST[7..0] + SRC[7..0];

* repeat add operation for 2nd through 7th byte *;

DEST[63..56] \leftarrow DEST[63..56] + SRC[63..56];

PADDB instruction with 128-bit operands:

DEST[7-0] \leftarrow DEST[7-0] + SRC[7-0]:

* repeat add operation for 2nd through 14th byte *;

DEST[127-120] \leftarrow DEST[111-120] + SRC[127-120];

PADDW instruction with 64-bit operands:

DEST[15..0] \leftarrow DEST[15..0] + SRC[15..0];

* repeat add operation for 2nd and 3th word *;

DEST[63..48] \leftarrow DEST[63..48] + SRC[63..48];

PADDW instruction with 128-bit operands:

DEST[15-0] \leftarrow DEST[15-0] + SRC[15-0];

* repeat add operation for 2nd through 7th word *;

DEST[127-112] \leftarrow DEST[127-112] + SRC[127-112];

PADDD instruction with 64-bit operands:

DEST[31..0] \leftarrow DEST[31..0] + SRC[31..0];

DEST[63..32] \leftarrow DEST[63..32] + SRC[63..32];

PADDD instruction with 128-bit operands:

DEST[31-0] \leftarrow DEST[31-0] + SRC[31-0];

* repeat add operation for 2nd and 3th doubleword *;

DEST[127-96] \leftarrow DEST[127-96] + SRC[127-96];

同等のインテル® C/C++ コンパイラ組み込み関数

__m64 _mm_add_pi8(__m64 m1, __m64 m2)

PADDB

PADDB

__m128i_mm_add_epi8 (__m128ia,__m128ib )

__m64 _mm_addw_pi16(__m64 m1, __m64 m2)

PADDW

PADDW

__m128i _mm_add_epi16 ( __m128i a, __m128i b)

__m64 _mm_add_pi32(__m64 m1, __m64 m2)

PADDD

PADDD

__m128i _mm_add_epi32 ( __m128i a, __m128i b)

```

### 影響を受けるフラグ

なし。

# PADDB/PADDW/PADDD—Add Packed Integers (続き)

## 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CRO の EM がセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX® テクノロジ対応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

## 実アドレスモード例外

#GP (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合。

#UD CR0 の EM がセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

# 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

# PADDQ—Add Packed Quadword Integers

| オペコード       | 命令                    | 説明                                                       |

|-------------|-----------------------|----------------------------------------------------------|

| 0F D4 /r    | PADDQ mm1, mm2/m64    | mm2/m64 と mm1 のクワッドワード整数を加算し、<br>結果を mm1 に格納する。          |

| 66 0F D4 /r | PADDQ xmm1, xmm2/m128 | xmm2/m128 と xmm1 のパックド・クワッドワード<br>整数を加算し、結果を xmm1 に格納する。 |

### 説明

第1オペランド (デスティネーション・オペランド) と第2オペランド (ソース・オペランド) を加算して、結果をデスティネーション・オペランドに格納する。ソース・オペランドは、MMX® テクノロジ・レジスタまたは64 ビットのメモリ・ロケーションに格納される1つのクワッドワード整数か、XMM レジスタまたは128 ビットのメモリ・ロケーションに格納される2つのパックド・クワッドワード整数である。デスティネーション・オペランドは、MMX テクノロジ・レジスタに格納される1つのクワッドワード整数か、XMM レジスタに格納される2つのパックド・クワッドワード整数である。パックド・クワッドワードのオペランドを使用する場合は、SIMD 加算が実行される。結果のクワッドワードが大きすぎて64 ビットで表現できない場合は(オーバーフロー)、結果はラップアラウンドされ、下位64 ビットがデスティネーション要素に書き込まれる(すなわち、キャリーは無視される)。

PADDQ命令は、符号なし整数と符号付き整数 (2の補数記法) のどちらを操作することもできる。ただし、この命令は、オーバーフローやキャリーを示す EFLAGS レジス タ内のビットをセットしない。このため、検出されないオーバーフロー状態が発生しないように、操作される値の範囲をソフトウェアによって制御しなければならない。

## 操作

PADDQ instruction with 64-Bit operands: DEST[63-0] DEST[63-0] + SRC[63-0];

PADDQ instruction with 128-Bit operands: DEST[63-0] " DEST[63-0] + SRC[63-0]; DEST[127-64] " DEST[127-64] + SRC[127-64];

# 同等のインテル® C/C++ コンパイラ組み込み関数

PADDQ \_\_m64 \_mm\_add\_si64 (\_\_m64 a, \_\_m64 b)

PADDQ \_\_m128i \_mm\_add\_epi64 ( \_\_m128i a, \_\_m128i b)

# 影響を受けるフラグ

なし。

# PADDQ—Add Packed Quadword Integers (続き)

# 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが、CS、DS、ES、FS、またはGS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CR0 の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックが有効になっており、

現行特権レベルが3のときにアライメントの合っていないメモリ参照

を行った場合。

# 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

オペランドの一部が0~FFFFHの実効アドレス空間の範囲外の場合。

#UD CR0 の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックが有効になっており、

アライメントの合っていないメモリ参照を行った場合。

# 数值例外

なし。

# PADDSB/PADDSW—Add Packed Signed Integers with Signed Saturation

| オペコード       | 命令                     | 説明                                                    |

|-------------|------------------------|-------------------------------------------------------|

| OF EC /r    | PADDSB mm, mm/m64      | <i>mm/m64 と mm のパックド符号付きバイト</i> 整数を<br>加算し、結果を飽和処理する。 |

| 66 0F EC /r | PADDSB xmm1, xmm2/m128 | xmm2/m128 と xmm1 のパックド符号付きバイト<br>整数を加算し、結果を飽和処理する。    |

| OF ED /r    | PADDSW mm, mm/m64      | mm/m64 と mm のパックド符号付きワード整数を<br>加算し、結果を飽和処理する。         |

| 66 0F ED /r | PADDSW xmm1, xmm2/m128 | xmm2/m128 と xmm1 のパックド符号付きワード<br>整数を加算し、結果を飽和処理する。    |

# 説明

ソース・オペランド(第2オペランド)とデスティネーション・オペランド(第1オペランド)のパックド符号付き整数の SIMD 加算を実行し、結果のパックド整数をデスティネーション・オペランドに格納する。SIMD 演算の図は、『IA-32インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、上巻』の図9-4.を参照のこと。以降の段落で説明するように、オーバーフローは符号付き飽和処理を使用して処理される。

上記の命令は、64 ビット・オペランドまたは128 ビット・オペランドのいずれかを操作する。64 ビット・オペランドを操作する場合、デスティネーション・オペランドには MMX®テクノロジ・レジスタを使用しなければならないが、ソース・オペランドには MMX テクノロジ・レジスタまたは64 ビット・メモリ・ロケーションのどちらを使用しても構わない。128 ビット・オペランドを操作する場合は、デスティネーション・オペランドには XMM レジスタを使用しなければならないが、ソース・オペランドには XMM レジスタまたは128 ビット・メモリ・ロケーションのどちらを使用しても構わない。

PADDSB命令は、パックド符号付きバイト整数を加算する。個別のバイトの結果が符号付きバイト整数の範囲を超える場合(すなわち、7FHより大きいかまたは80Hより小さい場合)は、それぞれ7FHまたは80Hの飽和された値がデスティネーション・オペランドに書き込まれる。

PADDSW命令は、パックド符号付きワード整数を加算する。個別のワードの結果が符号付きワード整数の範囲を超える場合(すなわち、7FFFHより大きいかまたは8000Hより小さい場合)は、それぞれ7FFFHまたは8000Hの飽和された値がデスティネーション・オペランドに書き込まれる。

# PADDSB/PADDSW—Add Packed Signed Integers with Signed Saturation (続き)

# 操作

```

PADDSB instruction with 64-bit operands:

DEST[7..0] \leftarrow SaturateToSignedByte(DEST[7..0] + SRC (7..0]);

* repeat add operation for 2nd through 7th bytes *;

DEST[63..56] \leftarrow SaturateToSignedByte(DEST[63..56] + SRC[63..56]);

PADDSB instruction with 128-bit operands:

DEST[7-0] ← SaturateToSignedByte (DEST[7-0] + SRC[7-0]);

* repeat add operation for 2nd through 14th bytes *;

DEST[127-120] \leftarrow SaturateToSignedByte (DEST[111-120] + SRC[127-120]);

PADDSW instruction with 64-bit operands

DEST[15..0] ← SaturateToSignedWord(DEST[15..0] + SRC[15..0]);

* repeat add operation for 2nd and 7th words *;

DEST[63..48] \leftarrow SaturateToSignedWord(DEST[63..48] + SRC[63..48]);

PADDSW instruction with 128-bit operands

DEST[15-0] \leftarrow SaturateToSignedWord (DEST[15-0] + SRC[15-0]);

* repeat add operation for 2nd through 7th words *;

DEST[127-112] \leftarrow SaturateToSignedWord (DEST[127-112] + SRC[127-112]);

同等のインテル® C/C++ コンパイラ組み込み関数

__m64 _mm_adds_pi8(__m64 m1, __m64 m2)

PADDSB

```

# 影響を受けるフラグ

なし。

PADDSB

PADDSW

PADDSW

### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

\_\_m128i \_mm\_adds\_epi8 ( \_\_m128i a, \_\_m128i b)

\_\_m128i \_mm\_adds\_epi16 ( \_\_m128i a, \_\_m128i b)

\_\_m64 \_mm\_adds\_pi16(\_\_m64 m1, \_\_m64 m2)

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD  $CR0 \circ EM \circ t$  がセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が 発生する。SSE2 に対応していないプロセッサ ( $MMX^{®}$  テクノロジ対 応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

# PADDSB/PADDSW—Add Packed Signed Integers with Signed Saturation (続き)

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

# 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合。

#UD CRO の EM がセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX® テクノロジ対応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

# PADDUSB/PADDUSW—Add Packed Unsigned Integers with Unsigned Saturation

| オペコード       | 命令                      | 説明                                                       |

|-------------|-------------------------|----------------------------------------------------------|

| 0F DC /r    | PADDUSB mm, mm/m64      | mm/m64 と mm のパックド符号なしバイト整数<br>を加算し、結果を飽和処理する。            |

| 66 0F DC /r | PADDUSB xmm1, xmm2/m128 | <i>xmm2/m128と xmm1</i> のパックド符号なしバイト<br>整数を加算し、結果を飽和処理する。 |

| 0F DD /r    | PADDUSW mm, mm/m64      | mm/m64 と mm のパックド符号なしワード整数<br>を加算し、結果を飽和処理する。            |

| 66 0F DD /r | PADDUSW xmm1, xmm2/m128 | xmm2/m128と xmm1のパックド符号なしワード<br>整数を加算し、結果を飽和処理する。         |

#### 説明

ソース・オペランド(第2オペランド)とデスティネーション・オペランド(第1オペランド)のパックド符号なし整数の SIMD 加算を実行し、結果のパックド整数をデスティネーション・オペランドに格納する。SIMD 演算の図は、『IA-32インテル® アーキテクチャ・ソフトウェア・デベロッパーズ・マニュアル、上巻』の図9-4.を参照のこと。以降の段落で説明するように、オーバーフローは符号なし飽和処理を使用して処理される。

上記の命令は、64 ビット・オペランドまたは128 ビット・オペランドのいずれかを操作する。64 ビット・オペランドを操作する場合、デスティネーション・オペランドにはMMX®テクノロジ・レジスタを使用しなければならないが、ソース・オペランドにはMMXテクノロジ・レジスタまたは64 ビット・メモリ・ロケーションのどちらを使用しても構わない。128 ビット・オペランドを操作する場合は、デスティネーション・オペランドには XMM レジスタを使用しなければならないが、ソース・オペランドには XMM レジスタまたは128 ビット・メモリ・ロケーションのどちらを使用しても構わない。

PADDUSB 命令は、パックド符号なしバイト整数を加算する。個別のバイトの結果が符号なしバイト整数の範囲を超える場合(すなわち、FFHより大きい場合)は、FFHの飽和された符号なし値がデスティネーション・オペランドに書き込まれる。

PADDUSW命令は、パックド符号なしワード整数を加算する。個別のワードの結果が符号なしワード整数の範囲を超える場合(すなわち、FFFFHより大きい場合)は、FFFFHの飽和された符号なし値がデスティネーション・オペランドに書き込まれる。

# PADDUSB/PADDUSW—Add Packed Unsigned Integers with Unsigned Saturation (続き)

#### 操作

```

PADDUSB instruction with 64-bit operands:

```

$DEST[7..0] \leftarrow SaturateToUnsignedByte(DEST[7..0] + SRC (7..0]);$

\* repeat add operation for 2nd through 7th bytes \*:

DEST[63..56] ← SaturateToUnsignedByte(DEST[63..56] + SRC[63..56]

#### PADDUSB instruction with 128-bit operands:

DEST[7-0]  $\leftarrow$  SaturateToUnsignedByte (DEST[7-0] + SRC[7-0]);

\* repeat add operation for 2nd through 14th bytes \*:

$DEST[127-120] \leftarrow SaturateToUnSignedByte (DEST[127-120] + SRC[127-120]);$

#### PADDUSW instruction with 64-bit operands:

```

DEST[15..0] \leftarrow SaturateToUnsignedWord(DEST[15..0] + SRC[15..0]);

```

\* repeat add operation for 2nd and 3rd words \*:

$DEST[63..48] \leftarrow SaturateToUnsignedWord(DEST[63..48] + SRC[63..48]);$

#### PADDUSW instruction with 128-bit operands:

DEST[15-0] ← SaturateToUnsignedWord (DEST[15-0] + SRC[15-0]);

\* repeat add operation for 2nd through 7th words \*:

DEST[127-112] ← SaturateToUnSignedWord (DEST[127-112] + SRC[127-112]);

#### 同等のインテル® C/C++ コンパイラ組み込み関数

```

PADDUSB __m64 _mm_adds_pu8(__m64 m1, __m64 m2)

PADDUSW __m64 _mm_adds_pu16(__m64 m1, __m64 m2)

PADDUSB __m128i _mm_adds_epu8 ( __m128i a, __m128i b)

PADDUSW __m128i _mm_adds_epu16 ( __m128i a, __m128i b)

```

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD  $CR0 \circ EM \circ t$  がセットされた場合。

CR4の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

# PADDUSB/PADDUSW—Add Packed Unsigned Integers with Unsigned Saturation (続き)

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

#### 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合。

#UD CRO の EM がセットされた場合。

(CR4のOSFXSRが0の場合にのみ、128ビット操作によって#UDが発生する。SSE2に対応していないプロセッサ (MMX テクノロジ対応プロセッサ)上で128ビット命令を実行した場合、その命令はmm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

#### 数值例外

## **PAND—Logical AND**

| オペコード       | 命令                   | 説明                                              |

|-------------|----------------------|-------------------------------------------------|

| 0F DB /r    | PAND mm, mm/m64      | <i>mm/m64 と mm</i> のビット単位の AND(論理積)演算<br>を実行する。 |

| 66 0F DB /r | PAND xmm1, xmm2/m128 | xmm2/m128 と xmm1 のビット単位の AND(論理積)<br>演算を実行する。   |

#### 説明

ソース・オペランド(第2オペランド)とデスティネーション・オペランド(第1オペランド)との間のビット単位の AND(論理積)演算を実行し、結果をデスティネーション・オペランドにストアする。ソース・オペランドには、MMX®テクノロジ・レジスタか 64 ビット・メモリ・ロケーションを使用でき、または XMM レジスタか 128 ビット・メモリ・ロケーションを使用できる。デスティネーション・オペランドは、MMX テクノロジ・レジスタまたは XMM レジスタでなければならない。各ビットの結果は、第1と第2オペランドの対応するビットが両方とも1である場合は1にセットされ、そうでない場合はゼロにセットされる。

#### 操作

DEST ← DEST AND SRC;

#### 同等のインテル® C/C++ コンパイラ組み込み関数

PAND \_\_m64 \_mm\_and\_si64 (\_\_m64 m1, \_\_m64 m2)

PAND \_\_m128i \_mm\_and\_si128 ( \_\_m128i a, \_\_m128i b)

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CR0 の EM がセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ)上で128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

# PAND—Logical AND(続き)

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

#### 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合。

#UD CR0 の EM がセットされた場合。

CR4の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

#### 数值例外

## **PANDN—Logical AND NOT**

| オペコード       | 命令                    | 説明                                                             |

|-------------|-----------------------|----------------------------------------------------------------|

| 0F DF /r    | PANDN mm, mm/m64      | <i>mm/m64</i> と <i>mm</i> のビット単位の AND NOT (否定論理<br>積) 演算を実行する。 |

| 66 0F DF /r | PANDN xmm1, xmm2/m128 | xmm2/m128 と xmm1 のビット単位の AND NOT(否<br>定論理積)演算を実行する。            |

#### 説明

デスティネーション・オペランド (第1オペランド) のビット単位のNOT (否定) 演算を実行した後、反転されたデスティネーション・オペランドとソース・オペランド (第2オペランド) の間でビット単位のAND (論理積) 演算を実行する。結果はデスティネーション・オペランドに格納される。ソース・オペランドは、MMX®テクノロジ・レジスタまたは64ビットのメモリ・ロケーションか、XMM レジスタまたは128ビットのメモリ・ロケーションである。デスティネーション・オペランドは、MMX テクノロジ・レジスタまたはXMM レジスタである。結果の各ビットは、第1オペランド内の対応するビットが0で第2オペランド内の対応するビットが1の場合は1に設定され、それ以外の場合は0に設定される。

#### 操作

$DEST \leftarrow (NOT DEST) AND SRC;$

#### 同等のインテル® C/C++ コンパイラ組み込み関数

PANDN \_\_m64 \_mm\_andnot\_si64 (\_\_m64 m1, \_\_m64 m2)

PANDN \_\_m128i \_mm\_andnot\_si128 ( \_\_m128i a, \_\_m128i b)

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CR0 O EM がセットされた場合。

CR4の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

# PANDN—Logical AND NOT (続き)

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが3のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

#### 実アドレスモード例外

#GP (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合。

#UD CR0 の EM がセットされた場合。

CR4の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ)上で128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

#### 数值例外

# **PAUSE—Spin Loop Hint**

| オペコード | 命令    | 説明                                                |

|-------|-------|---------------------------------------------------|

| F3 90 | PAUSE | spin-wait ループのパフォーマンスを向上させるためのヒ<br>ントをプロセッサに提供する。 |

#### 説明

spin-wait ループのパフォーマンスを向上させる。「spin-wait ループ」を実行すると、インテル® Pentium® 4プロセッサまたはインテル® Xeon™ プロセッサは起こり得るメモリ順序違反を検出したとき、パフォーマンスの面で厳しい制限を受ける。PAUSE命令は、コード・シーケンスが spin-wait ループになっているプロセッサにヒントを提供する。プロセッサはこのヒントを使用して、大抵の状況におけるメモリ順序違反を回避する。これにより、プロセッサのパフォーマンスは大幅に向上する。こうした理由により、PAUSE命令をすべての spin-wait ループに配置することが推奨される。

PAUSE 命令は、spin ループの実行時にインテル Pentium 4 プロセッサの消費電力を低減させる追加機能を備えている。インテル Pentium 4 プロセッサは spin-wait ループを極めて高速に実行できるため、リソースの待機中に電力を大量に消費する。spin-wait ループに PAUSE 命令を挿入することで、プロセッサの消費電力が大幅に低減される。

この命令はインテル Pentium 4プロセッサで導入されたが、すべての IA-32 プロセッサに対して互換性がある。初期の IA-32 プロセッサにおいては、PAUSE 命令は NOP 命令と同じような動作をする。インテル Pentium 4プロセッサとインテル Xeon プロセッサは、事前定義された待ち時間として PAUSE 命令を実装している。この待ち時間は有限であり、プロセッサによってはゼロである場合もある。この命令は、プロセッサのアーキテクチャ上の状態を変更することはない(つまり、この命令は、基本的には、ノー・オペレーションを実行することで次の命令の実行を遅らせる)。

#### 操作

Execute\_Next\_Instruction(DELAY);

保護モード例外

なし。

実アドレスモード例外

なし。

仮想 8086 モード例外

# PAUSE—Spin Loop Hint(続き)

数值例外

なし。

4-41

### PAVGB/PAVGW—Average Packed Integers

| オペコード        | 命令                    | 説明                                                          |

|--------------|-----------------------|-------------------------------------------------------------|

| 0F E0 /r     | PAVGB mm1, mm2/m64    | 丸めを使用して、 <i>mm2/m64 と mm1</i> のパックド符号<br>なしバイト整数の平均を求める。    |

| 66 0F E0, /r | PAVGB xmm1, xmm2/m128 | 丸めを使用して、 <i>xmm2/m128 と xmm1</i> のパックド<br>符号なしバイト整数の平均を求める。 |

| 0F E3 /r     | PAVGW mm1, mm2/m64    | 丸めを使用して、 <i>mm2/m64 と mm1</i> のパックド符号<br>なしワード整数の平均を求める。    |

| 66 0F E3 /r  | PAVGW xmm1, xmm2/m128 | 丸めを使用して、 <i>xmm2/m128 と xmm1</i> のパックド<br>符号なしワード整数の平均を求める。 |

#### 説明

ソース・オペランド (第2オペランド) とデスティネーション・オペランド (第1オペランド)のパックド符号なし整数の SIMD 平均値計算を実行し、結果をデスティネーション・オペランドに格納する。第1オペランドと第2オペランドの対応するデータ要素の各ペアについて、データ要素同士を加算して、その和に1を加算し、結果を1ビット右にシフトする。ソース・オペランドは、MMX®テクノロジ・レジスタまたは64ビットのメモリ・ロケーションか、XMM レジスタまたは128 ビットのメモリ・ロケーションである。デスティネーション・オペランドは、MMX テクノロジ・レジスタまたはXMM レジスタである。

PAVGB 命令は、符号なしパックドバイトを処理する。PAVGW 命令は、符号なしパックドワードを処理する。

#### 操作

PAVGB instruction with 64-bit operands:

$SRC[7-0) \leftarrow (SRC[7-0) + DEST[7-0) + 1) >> 1$ ; \* temp sum before shifting is 9 bits \* repeat operation performed for bytes 2 through 6;  $SRC[63-56) \leftarrow (SRC[63-56) + DEST[63-56) + 1) >> 1$ ;

PAVGW instruction with 64-bit operands:

$SRC[15-0) \leftarrow (SRC[15-0) + DEST[15-0) + 1) >> 1$ ; \* temp sum before shifting is 17 bits \* repeat operation performed for words 2 and 3;  $SRC[63-48) \leftarrow (SRC[63-48) + DEST[63-48) + 1) >> 1$ ;

PAVGB instruction with 128-bit operands:

$SRC[7-0) \leftarrow (SRC[7-0) + DEST[7-0) + 1) >> 1$ ; \* temp sum before shifting is 9 bits \* repeat operation performed for bytes 2 through 14;  $SRC[63-56) \leftarrow (SRC[63-56) + DEST[63-56) + 1) >> 1$ ;

PAVGW instruction with 128-bit operands:

SRC[15-0)  $\leftarrow$  (SRC[15-0) + DEST[15-0) + 1) >> 1; \* temp sum before shifting is 17 bits \* repeat operation performed for words 2 through 6; SRC[127-48)  $\leftarrow$  (SRC[127-112) + DEST[127-112) + 1) >> 1;

# PAVGB/PAVGW—Average Packed Integers (続き)

#### 同等のインテル® C/C++ コンパイラ組み込み関数

PAVGB \_\_m64\_mm\_avg\_pu8 (\_\_m64 a, \_\_m64 b)

PAVGW \_\_m64\_mm\_avg\_pu16 (\_\_m64 a, \_\_m64 b)

PAVGB \_\_m128i \_mm\_avg\_epu8 ( \_\_m128i a, \_\_m128i b)

PAVGW \_\_m128i \_mm\_avg\_epu16 ( \_\_m128i a, \_\_m128i b)

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CR0 の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

### 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

オペランドの一部が0~FFFFHの実効アドレス空間の範囲外の場合。

#UD CRO の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

# PAVGB/PAVGW—Average Packed Integers (続き)

#### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

#### 数值例外

## PCMPEQB/PCMPEQW/PCMPEQD—Compare Packed Data for Equal

| オペコード       | 命令                      | 説明                                            |

|-------------|-------------------------|-----------------------------------------------|

| 3 1         | HP 12                   | DC-51                                         |

| 0F 74 /r    | PCMPEQB mm, mm/m64      | mm/m64 と mm のパックドバイトを等しいか比<br>較する。            |

| 66 0F 74 /r | PCMPEQB xmm1, xmm2/m128 | xmm2/m128と xmm1 のパックドバイトを等しい<br>か比較する。        |

| 0F 75 /r    | PCMPEQW mm, mm/m64      | <i>mm/m64 と mm のパックドワードを</i> 等しいか比<br>較する。    |

| 66 0F 75 /r | PCMPEQW xmm1, xmm2/m128 | xmm2/m128と xmm1 のパックドワードを等しい<br>か比較する。        |

| 0F 76 /r    | PCMPEQD mm, mm/m64      | <i>mm/m64 と mm</i> のパックド・ダブルワードを等<br>しいか比較する。 |

| 66 0F 76 /r | PCMPEQD xmm1, xmm2/m128 | xmm2/m128 と xmm1 のパックド・ダブルワード<br>を等しいか比較する。   |

#### 説明

デスティネーション・オペランド (第1オペランド) とソース・オペランド (第2オペランド) のパックドバイト/ワード/ダブルワードが等しいかどうかの SIMD 比較を実行する。データ要素のペアが等しい場合は、デスティネーション・オペランドの対応するデータ要素はすべて1に設定される。そうでない場合は、すべてゼロに設定される。ソース・オペランドは、MMX® テクノロジ・レジスタまたは64 ビットのメモリ・ロケーション、XMM レジスタまたは128 ビットのメモリ・ロケーションを使用できる。デスティネーション・オペランドには、MMX テクノロジ・レジスタまたはXMM レジスタを使用できる。

PCMPEQB 命令は、デスティネーション・オペランドおよびソース・オペランドの対応するバイトを比較する。PCMPEQW 命令は、デスティネーション・オペランドおよびソース・オペランドの対応するワードを比較する。PCMPEQD 命令は、デスティネーション・オペランドおよびソース・オペランドの対応するダブルワードを比較する。

#### 操作

```

PCMPEQB instruction with 64-bit operands:

```

```

\begin{aligned} \text{IF DEST}[7..0] &= \text{SRC}[7..0] \\ \text{THEN DEST}[7 \ 0) &\leftarrow \text{FFH}; \\ \text{ELSE DEST}[7..0] &\leftarrow 0; \end{aligned}

```

\* Continue comparison of 2nd through 7th bytes in DEST and SRC \*

IF DEST[63..56] = SRC[63..56] THEN DEST[63..56]  $\leftarrow$  FFH; ELSE DEST[63..56]  $\leftarrow$  0;

PCMPEQB instruction with 128-bit operands:

```

IF DEST[7..0] = SRC[7..0]

THEN DEST[7 0) \leftarrow FFH;

ELSE DEST[7..0] \leftarrow 0;

```

# PCMPEQB/PCMPEQW/PCMPEQD—Compare Packed Data for Equal (続き)

```

* Continue comparison of 2nd through 15th bytes in DEST and SRC *

IF DEST[63..56] = SRC[63..56]

THEN DEST[63..56] \leftarrow FFH;

ELSE DEST[63..56] \leftarrow 0;

PCMPEQW instruction with 64-bit operands:

IF DEST[15..0] = SRC[15..0]

THEN DEST[15..0] ← FFFFH;

ELSE DEST[15..0] \leftarrow 0;

* Continue comparison of 2nd and 3rd words in DEST and SRC *

IF DEST[63..48] = SRC[63..48]

THEN DEST[63..48] \leftarrow FFFFH;

ELSE DEST[63..48] \leftarrow 0;

PCMPEQW instruction with 128-bit operands:

IF DEST[15..0] = SRC[15..0]

THEN DEST[15..0] ← FFFFH;

ELSE DEST[15..0] \leftarrow 0;

* Continue comparison of 2nd through 7th words in DEST and SRC *

IF DEST[63..48] = SRC[63..48]

THEN DEST[63..48] ← FFFFH;

ELSE DEST[63..48] \leftarrow 0;

PCMPEQD instruction with 64-bit operands:

IF DEST[31..0] = SRC[31..0]

THEN DEST[31..0] ← FFFFFFFH;

ELSE DEST[31..0] \leftarrow 0;

IF DEST[63..32] = SRC[63..32]

THEN DEST[63..32] \leftarrow FFFFFFFH;

ELSE DEST[63..32] \leftarrow 0;

PCMPEQD instruction with 128-bit operands:

IF DEST[31..0] = SRC[31..0]

THEN DEST[31..0] ← FFFFFFFH;

ELSE DEST[31..0] \leftarrow 0;

* Continue comparison of 2nd and 3rd doublewords in DEST and SRC *

IF DEST[63..32] = SRC[63..32]

THEN DEST[63..32] ← FFFFFFFH;

ELSE DEST[63..32] \leftarrow 0;

```

# PCMPEQB/PCMPEQW/PCMPEQD—Compare Packed Data for Equal (続き)

#### 同等のインテル® C/C++ コンパイラ組み込み関数

PCMPEQB

\_m64 \_mm\_cmpeq\_pi8 (\_\_m64 m1, \_\_m64 m2)

PCMPEQW

\_m64 \_mm\_cmpeq\_pi16 (\_\_m64 m1, \_\_m64 m2)

PCMPEQD

\_m64 \_mm\_cmpeq\_pi32 (\_\_m64 m1, \_\_m64 m2)

PCMPEQB

\_m128i \_mm\_cmpeq\_epi8 ( \_\_m128i a, \_\_m128i b)

PCMPEQW

\_m128i \_mm\_cmpeq\_epi16 ( \_\_m128i a, \_\_m128i b)

PCMPEQD

\_m128i \_mm\_cmpeq\_epi32 ( \_\_m128i a, \_\_m128i b)

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CRO の EM がセットされた場合。

CR4の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が 発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対 応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM  $CR0 \circ TS$ がセットされた場合。

#MF (64 ビット操作のみ) 未処理の X87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

# PCMPEQB/PCMPEQW/PCMPEQD—Compare Packed Data for Equal (続き)

#### 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合。

#UD CROのEMがセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ) 上で 128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の X87 FPU 例外がある場合。

#### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

#### 数值例外

# PCMPGTB/PCMPGTW/PCMPGTD—Compare Packed Signed Integers for Greater Than

| オペコード       | 命令                      | 説明                                                    |

|-------------|-------------------------|-------------------------------------------------------|

| 0F 64 /r    | PCMPGTB mm, mm/m64      | mm と mm/m64 のパックド符号付きバイト整数<br>を、「より大きい」の条件で比較する。      |

| 66 0F 64 /r | PCMPGTB xmm1, xmm2/m128 | xmm1とxmm2/m128のパックド符号付きバイト<br>整数を、「より大きい」の条件で比較する。    |

| 0F 65 /r    | PCMPGTW mm, mm/m64      | mm と mm/m64 のパックド符号付きワード整数<br>を、「より大きい」の条件で比較する。      |

| 66 0F 65 /r | PCMPGTW xmm1, xmm2/m128 | xmm1とxmm2/m128のパックド符号付きワード<br>整数を、「より大きい」の条件で比較する。    |

| 0F 66 /r    | PCMPGTD mm, mm/m64      | mm と mm/m64 のパックド符号付きダブルワー<br>ド整数を、「より大きい」の条件で比較する。   |

| 66 0F 66 /r | PCMPGTD xmm1, xmm2/m128 | xmm1とxmm2/m128のパックド符号付きダブル<br>ワード整数を、「より大きい」の条件で比較する。 |

#### 説明

デスティネーション・オペランド (第1オペランド) のパックドバイト整数/ワード整数/ダブルワード整数の値が、ソース・オペランド (第2オペランド) のパックドバイト整数/ワード整数/ダブルワード整数の値より大きいかどうかの SIMD 符号付き比較を実行する。デスティネーション・オペランドのデータ要素がソース・オペランドの対応するデータ要素より大きい場合は、デスティネーション・オペランドの対応するデータ要素はすべて1に設定される。そうでない場合は、すべて0に設定される。ソース・オペランドは、MMX® テクノロジ・レジスタまたは64 ビットのメモリ・ロケーション、XMM レジスタまたは128 ビットのメモリ・ロケーションを使用できる。デスティネーション・オペランドには、MMX テクノロジ・レジスタまたは XMM レジスタを使用できる。

PCMPGTB 命令は、デスティネーション・オペランドおよびソース・オペランドの対応する符号付きバイト整数を比較する。PCMPGTW 命令は、デスティネーション・オペランドおよびソース・オペランドの対応する符号付きワード整数を比較する。PCMPGTD 命令は、デスティネーション・オペランドおよびソース・オペランドの対応する符号付きダブルワード整数を比較する。

#### 操作

PCMPGTB instruction with 64-bit operands:

$$\begin{split} \text{IF DEST}[7..0] > & \text{SRC}[7..0] \\ & \text{THEN DEST}[7 \ 0) \leftarrow \text{FFH}; \\ & \text{ELSE DEST}[7..0] \leftarrow 0; \end{split}$$

\* Continue comparison of 2nd through 7th bytes in DEST and SRC \*

IF DEST[63..56] > SRC[63..56] THEN DEST[63..56]  $\leftarrow$  FFH; ELSE DEST[63..56]  $\leftarrow$  0;

# PCMPGTB/PCMPGTW/PCMPGTD—Compare Packed Signed Integers for Greater Than (続き)

```

PCMPGTB instruction with 128-bit operands:

IF DEST[7..0] > SRC[7..0]

THEN DEST[7 0) \leftarrow FFH;

ELSE DEST[7..0] \leftarrow 0;

* Continue comparison of 2nd through 15th bytes in DEST and SRC *

IF DEST[63..56] > SRC[63..56]

THEN DEST[63..56] \leftarrow FFH;

ELSE DEST[63..56] \leftarrow 0;

PCMPGTW instruction with 64-bit operands:

IF DEST[15..0] > SRC[15..0]

THEN DEST[15..0] ← FFFFH;

ELSE DEST[15..0] \leftarrow 0;

* Continue comparison of 2nd and 3rd words in DEST and SRC *

IF DEST[63..48] > SRC[63..48]

THEN DEST[63..48] \leftarrow FFFFH;

ELSE DEST[63..48] \leftarrow 0;

PCMPGTW instruction with 128-bit operands:

IF DEST[15..0] > SRC[15..0]

THEN DEST[15..0] ← FFFFH;

ELSE DEST[15..0] \leftarrow 0;

* Continue comparison of 2nd through 7th words in DEST and SRC *

IF DEST[63..48] > SRC[63..48]

THEN DEST[63..48] \leftarrow FFFFH;

ELSE DEST[63..48] \leftarrow 0;

PCMPGTD instruction with 64-bit operands:

IF DEST[31..0] > SRC[31..0]

THEN DEST[31..0] ← FFFFFFFH;

ELSE DEST[31..0] \leftarrow 0;

IF DEST[63..32] > SRC[63..32]

THEN DEST[63..32] \leftarrow FFFFFFFH;

ELSE DEST[63..32] \leftarrow 0;

PCMPGTD instruction with 128-bit operands:

IF DEST[31..0] > SRC[31..0]

THEN DEST[31..0] ← FFFFFFFH;

ELSE DEST[31..0] \leftarrow 0;

* Continue comparison of 2nd and 3rd doublewords in DEST and SRC *

IF DEST[63..32] > SRC[63..32]

THEN DEST[63..32] \leftarrow FFFFFFFH;

ELSE DEST[63..32] \leftarrow 0;

```

# PCMPGTB/PCMPGTW/PCMPGTD—Compare Packed Signed Integers for Greater Than (続き)

#### 同等のインテル® C/C++ コンパイラ組み込み関数

PCMPGTB

\_\_m64 \_mm\_cmpgt\_pi8 (\_\_m64 m1, \_\_m64 m2)

PCMPGTW

\_\_m64 \_mm\_pcmpgt\_pi16 (\_\_m64 m1, \_\_m64 m2)

DCMPGTD

\_\_m64 \_mm\_pcmpgt\_pi32 (\_\_m64 m1, \_\_m64 m2)

PCMPGTB

\_\_m128i \_mm\_cmpgt\_epi8 ( \_\_m128i a, \_\_m128i b)

PCMPGTW

\_\_m128i \_mm\_cmpgt\_epi16 ( \_\_m128i a, \_\_m128i b)

DCMPGTD

\_\_m128i \_mm\_cmpgt\_epi32 ( \_\_m128i a, \_\_m128i b)

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CR0 の EM がセットされた場合。

CR4の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ)上で128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM  $CR0 \circ TS$ がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

# PCMPGTB/PCMPGTW/PCMPGTD—Compare Packed Signed Integers for Greater Than (続き)

#### 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合。

#UD CR0 の EM がセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ)上で128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

#### 数值例外

#### **PEXTRW—Extract Word**

| オペコード          | 命令                    | 説明                                          |

|----------------|-----------------------|---------------------------------------------|

| 0F C5 /r ib    | PEXTRW r32, mm, imm8  | imm8 によって指定されたワードを mm から抽出し、<br>r32 に移動する。  |

| 66 0F C5 /r ib | PEXTRW r32, xmm, imm8 | imm8 によって指定されたワードを xmm から抽出し、<br>r32 に移動する。 |

#### 説明

カウント・オペランド (第3オペランド) で指定されたソース・オペランド (第2オペランド) 内のワードを、デスティネーション・オペランド (第1オペランド) にコピーする。ソース・オペランドは、MMX®テクノロジ・レジスタまたはXMM レジスタである。デスティネーション・オペランドは汎用レジスタの下位ワードである。カウント・オペランドは8ビットの即値である。MMX テクノロジ・レジスタにワード・ロケーションを指定する場合、カウント・オペランドの下位2ビットによってそのロケーションを指定する。XMM レジスタの場合は、下位3ビットによってそのロケーションを指定する。デスティネーション・オペランドの上位ワードはクリアされる(すべて0に設定される)。

#### 操作

PEXTRW instruction with 64-bit source operand:

SEL  $\leftarrow$  COUNT AND 3H; TEMP  $\leftarrow$  (SRC >> (SEL \* 16)) AND FFFFH; r32[15-0]  $\leftarrow$  TEMP[15-0]; r32[31-16]  $\leftarrow$  0000H;

PEXTRW instruction with 128-bit source operand:

SEL  $\leftarrow$  COUNT AND 7H; TEMP  $\leftarrow$  (SRC >> (SEL \* 16)) AND FFFFH; r32[15-0]  $\leftarrow$  TEMP[15-0]; r32[31-16]  $\leftarrow$  0000H;

#### 同等のインテル® C/C++ コンパイラ組み込み関数

PEXTRW int\_mm\_extract\_pi16 (\_\_m64 a, int n)

PEXTRW int \_mm\_extract\_epi16 (\_\_m128i a, int imm)

#### 影響を受けるフラグ

#### PEXTRW—Extract Word (続き)

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CROのEMがセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

#### 実アドレスモード例外

#GP(0) オペランドの一部が $0 \sim FFFFH$ の実効アドレス空間の範囲外の場合。

#UD CROのEMがセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

#### 数值例外

#### PINSRW—Insert Word

| オペコード          | 命令                        | 説明                                                   |

|----------------|---------------------------|------------------------------------------------------|

| 0F C4 /r ib    | PINSRW mm, r32/m16, imm8  | r32 または m16 の下位ワードを、imm8 で指定さ<br>れた mm 内のワード位置に挿入する。 |

| 66 0F C4 /r ib | PINSRW xmm, r32/m16, imm8 | r32 または m16 の下位ワードを、imm8 で指定された xmm 内のワード位置に移動する。    |

#### 説明

ソース・オペランド (第2オペランド) から1ワードをコピーして、カウント・オペランド (第3オペランド) で指定されたデスティネーション・オペランド (第1オペランド) 内の位置に挿入する (デスティネーション・レジスタのその他のワードは変更されない)。ソース・オペランドは、汎用レジスタまたは16ビットのメモリ・ロケーションである (ソース・オペランドが汎用レジスタの場合は、レジスタの下位ワードがコピーされる)。デスティネーション・オペランドは、MMX®テクノロジ・レジスタまたはXMM レジスタである。カウント・オペランドは8ビットの即値である。MMXテクノロジ・レジスタにワード・ロケーションを指定する場合、カウント・オペランドの下位2ビットによってそのロケーションを指定する。XMM レジスタの場合は、下位3ビットによってそのロケーションを指定する。

#### 操作

```

PINSRW instruction with 64-bit source operand:

```

```

SEL ← COUNT AND 3H;

```

CASE (determine word position) OF

SEL  $\leftarrow$  0: MASK  $\leftarrow$  00000000000FFFFH:

SEL  $\leftarrow$  1: MASK  $\leftarrow$  00000000FFFF0000H;

SEL  $\leftarrow$  2: MASK  $\leftarrow$  0000FFFF00000000H:

SEL  $\leftarrow$  3: MASK  $\leftarrow$  FFFF000000000000H;

DEST ← (DEST AND NOT MASK) OR (((SRC << (SEL \* 16)) AND MASK);

PINSRW instruction with 128-bit source operand:

```

SEL ← COUNT AND 7H;

```

CASE (determine word position) OF

SEL ← 1: MASK ← 00000000000000000000000FFF0000H;

SEL  $\leftarrow$  2: MASK  $\leftarrow$  000000000000000000FFFF00000000H;

SEL  $\leftarrow$  3: MASK  $\leftarrow$  000000000000000FFFF00000000000H;

DEST ← (DEST AND NOT MASK) OR (((SRC << (SEL \* 16)) AND MASK);

#### PINSRW—Insert Word (続き)

#### 同等のインテル® C/C++ コンパイラ組み込み関数

PINSRW \_\_m64 \_mm\_insert\_pi16 (\_\_m64 a, int d, int n)

PINSRW \_\_m128i \_mm\_insert\_epi16 ( \_\_m128i a, int b, int imm)

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CR0 の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

#### 実アドレスモード例外

#GP(0) オペランドの一部が $0 \sim FFFFH$ の実効アドレス空間の範囲外の場合。

#UD CR0 の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

# PINSRW—Insert Word(続き)

数值例外

なし。

4-57

## PMADDWD—Multiply and Add Packed Integers

| オペコード       | 命令                      | 説明                                                                               |

|-------------|-------------------------|----------------------------------------------------------------------------------|

| 0F F5 /r    | PMADDWD mm, mm/m64      | mm のパックドワードに mm/m64 のパックド<br>ワードを掛ける。結果の隣接するダブルワード<br>を加算して mm にストアする。           |

| 66 0F F5 /r | PMADDWD xmm1, xmm2/m128 | xmm1 のパックドワード整数に xmm2/m128 の<br>パックドワード整数を掛けて、得られた隣接す<br>るダブルワードを加算してxmm1にストアする。 |

#### 説明

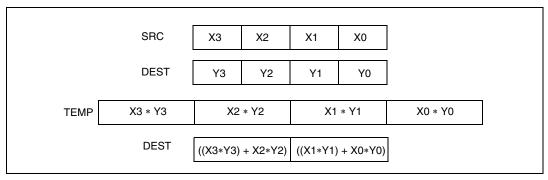

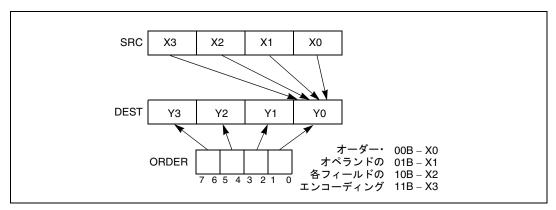

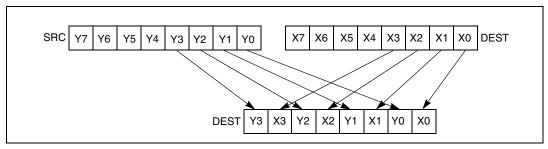

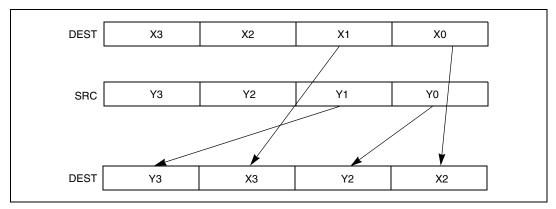

デスティネーション・オペランド (第 1 オペランド) の個別のパックド符号付きワードにソース・オペランド (第 2 オペランド) の対応する符号付きワードを掛け、仮の符号付きダブルワードの結果を生成する。次に、得られた隣接するダブルワードを合計して、デスティネーション・オペランドに格納する。例えば、ソース・オペランドとデスティネーション・オペランド内の対応する下位ワード ( $15\sim0$ ) および ( $31\sim16$ ) 同士がそれぞれ乗算されて、得られたダブルワードが加算され、デスティネーション・レジスタの下位ダブルワード ( $31\sim0$ ) に格納される。その他の隣接するワードについても、同じ操作が実行される (図 4-2. は、64 ビット・オペランドを使用する場合の操作を示している)。ソース・オペランドは、 $MMX^{®}$  テクノロジ・レジスタまたは 64 ビットのメモリ・ロケーションが、128 ビットのメモリ・ロケーションである。デスティネーション・オペランドは、128 ビットのメモリ・ロケーションである。

PMADD命令は、1つのグループ内の操作される2対のワードがすべて8000Hである場合にのみ、ラップアラウンドを使用する。この場合、結果は80000000Hにラップアラウンドされる。

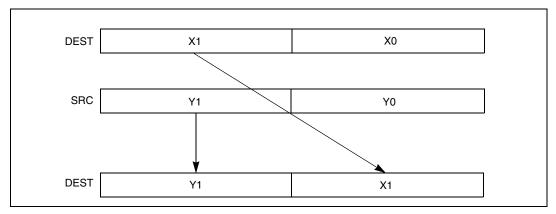

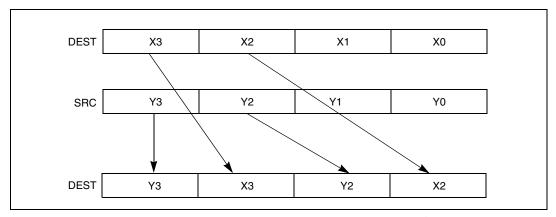

図 4-2. 64 ビット・オペランドを使用した PMADDWD 実行モデル

# PMADDWD-Multiply and Add Packed Integers (続き)

#### 操作

PMADDWD instruction with 64-bit operands:

```

DEST[31..0] \leftarrow (DEST[15..0] * SRC[15..0]) + (DEST[31..16] * SRC[31..16]);

DEST[63..32] \leftarrow (DEST[47..32] * SRC[47..32]) + (DEST[63..48] * SRC[63..48]);

```

PMADDWD instruction with 128-bit operands:

```

\begin{split} \mathsf{DEST}[31..0] \leftarrow (\mathsf{DEST}[15..0] * \mathsf{SRC}[15..0]) + (\mathsf{DEST}[31..16] * \mathsf{SRC}[31..16]); \\ \mathsf{DEST}[63..32] \leftarrow (\mathsf{DEST}[47..32] * \mathsf{SRC}[47..32]) + (\mathsf{DEST}[63..48] * \mathsf{SRC}[63..48]); \\ \mathsf{DEST}[95..64) \leftarrow (\mathsf{DEST}[79..64) * \mathsf{SRC}[79..64)) + (\mathsf{DEST}[95..80) * \mathsf{SRC}[95..80)); \\ \mathsf{DEST}[127..96) \leftarrow (\mathsf{DEST}[111..96) * \mathsf{SRC}[111..96)) + (\mathsf{DEST}[127..112) * \\ \mathsf{SRC}[127..112)); \end{split}

```

#### 同等のインテル® C/C++ コンパイラ組み込み関数

```

PMADDWD __m64 _mm_madd_pi16(__m64 m1, __m64 m2)

PMADDWD __m128i _mm_madd_epi16 ( __m128i a, __m128i b)

```

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CRO の EM がセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ)上で128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが3のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

## PMADDWD—Multiply and Add Packed Integers (続き)

#### 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

オペランドのいずれかの部分が実効アドレス空間 0~ FFFFH の外に

ある場合。

#UD CROのEMがセットされた場合。

CR4 の OSFXSR が 0 の場合にのみ、128 ビット操作によって #UD が発生する。SSE2 に対応していないプロセッサ (MMX テクノロジ対応プロセッサ)上で128 ビット命令を実行した場合、その命令は mm

レジスタを操作し、#UD は発生しない。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

#### 数值例外

## PMAXSW—Maximum of Packed Signed Word Integers

| オペコード       | 命令                     | 説明                                          |

|-------------|------------------------|---------------------------------------------|

| OF EE /r    | PMAXSW mm1, mm2/m64    | mm2/m64と mm1の符号付きワード整数を比較して最大値を返す。          |

| 66 0F EE /r | PMAXSW xmm1, xmm2/m128 | xmm2/m128 と xmm1 の符号付きワード整数を比<br>較して最大値を返す。 |

#### 説明

デスティネーション・オペランド (第1オペランド) とソース・オペランド (第2オペランド) のパックド符号付きワード整数の SIMD 比較を実行し、それぞれのワード整数のペアの最大値をデスティネーション・オペランドに返す。ソース・オペランドは、MMX®テクノロジ・レジスタまたは64 ビットのメモリ・ロケーションか、XMMレジスタまたは128 ビットのメモリ・ロケーションである。デスティネーション・オペランドは、MMXテクノロジ・レジスタまたはXMM レジスタである。

#### 操作

```

PMAXSW instruction for 64-bit operands:

IF DEST[15-0] > SRC[15-0]) THEN

(DEST[15-0] \leftarrow DEST[15-0];

ELSE

(DEST[15-0] \leftarrow SRC[15-0];

FΙ

* repeat operation for 2nd and 3rd words in source and destination operands *

IF DEST[63-48] > SRC[63-48]) THEN

(DEST[63-48] \leftarrow DEST[63-48];

ELSE

(DEST[63-48] \leftarrow SRC[63-48];

PMAXSW instruction for 128-bit operands:

IF DEST[15-0] > SRC[15-0]) THEN

(DEST[15-0] \leftarrow DEST[15-0];

FLSE

(DEST[15-0] \leftarrow SRC[15-0];

FΙ

* repeat operation for 2nd through 7th words in source and destination operands *

IF DEST[127-112] > SRC[127-112]) THEN

(DEST[127-112] \leftarrow DEST[127-112];

ELSE

(DEST[127-112] \leftarrow SRC[127-112];

FΙ

同等のインテル® C/C++ コンパイラ組み込み関数

```

```

PMAXSW __m64 _mm_max_pi16(__m64 a, __m64 b)

PMAXSW __m128i _mm_max_epi16 ( __m128i a, __m128i b)

```

# PMAXSW—Maximum of Packed Signed Word Integers (続き)

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD  $CR0 \circ EM \circ T$  がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

#### 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

オペランドの一部が $0 \sim FFFFH$ の実効アドレス空間の範囲外の場合。

#UD CR0 の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

### 仮想 8086 モード例外

実アドレスモードと同じ例外。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) アライメント・チェックがイネーブルにされて

いて、アライメントが合わないメモリ参照が行われた場合。

# PMAXSW—Maximum of Packed Signed Word Integers(続き)

数值例外

### PMAXUB—Maximum of Packed Unsigned Byte Integers

| オペコード       | 命令                     | 説明                                       |

|-------------|------------------------|------------------------------------------|

| 0F DE /r    | PMAXUB mm1, mm2/m64    | mm2/m64 と mm1 の符号なしバイト整数を比較し<br>て最大値を返す。 |

| 66 0F DE /r | PMAXUB xmm1, xmm2/m128 | xmm2/m128とxmm1の符号なしバイト整数を比較<br>して最大値を返す。 |

#### 説明

デスティネーション・オペランド(第1オペランド)とソース・オペランド(第2オ ペランド)のパックド符号なしバイト整数の SIMD 比較を実行し、それぞれのバイト 整数のペアの最大値をデスティネーション・オペランドに返す。ソース・オペランド は、MMX®テクノロジ・レジスタまたは64ビットのメモリ・ロケーションか、XMM レジスタまたは128ビットのメモリ・ロケーションである。デスティネーション・オ ペランドは、MMXテクノロジ・レジスタまたはXMM レジスタである。

#### 操作

```

PMAXUB instruction for 64-bit operands:

IF DEST[7-0] > SRC[17-0]) THEN

(DEST[7-0] \leftarrow DEST[7-0];

ELSE

(DEST[7-0] \leftarrow SRC[7-0];

FΙ

* repeat operation for 2nd through 7th bytes in source and destination operands *

IF DEST[63-56] > SRC[63-56]) THEN

(DEST[63-56] \leftarrow DEST[63-56];

ELSE

(DEST[63-56] \leftarrow SRC[63-56];

FΙ

PMAXUB instruction for 128-bit operands:

IF DEST[7-0] > SRC[17-0]) THEN

(DEST[7-0] \leftarrow DEST[7-0];

ELSE

(DEST[7-0] \leftarrow SRC[7-0];

FΙ

* repeat operation for 2nd through 15th bytes in source and destination operands *

IF DEST[127-120] > SRC[127-120]) THEN

(DEST[127-120] \leftarrow DEST[127-120];

FLSE

(DEST[127-120] \leftarrow SRC[127-120];

FΙ

同等のインテル® C/C++ コンパイラ組み込み関数

```

```

__m64 _mm_max_pu8(__m64 a, __m64 b)

PMAXUB

PMAXUB

__m128i _mm_max_epu8 ( __m128i a, __m128i b)

```

# PMAXUB—Maximum of Packed Unsigned Byte Integers (続き)

#### 影響を受けるフラグ

なし。

#### 保護モード例外

#GP(0) メモリ・オペランドの実効アドレスが CS、DS、ES、FS、または GS

セグメントの範囲外の場合。

(128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが16バイトに合っていない場合。

#SS(0) メモリ・オペランドの実効アドレスが SS セグメントの範囲外の場合。

#UD CROのEMがセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。

#MF (64 ビット操作のみ) 未処理の x87 FPU 例外がある場合。

#PF (フォルトコード) ページフォルトが発生した場合。

#AC(0) (64 ビット操作のみ) 現行特権レベルが 3 のときに、アライメント・

チェックがイネーブルにされていて、アライメントが合わないメモリ

参照が行われた場合。

#### 実アドレスモード例外

#GP(0) (128 ビット操作のみ) セグメントに関係なく、メモリ・オペランド

のアライメントが 16 バイトに合っていない場合。

オペランドの一部が $0 \sim FFFFH$ の実効アドレス空間の範囲外の場合。

#UD CR0 の EM がセットされた場合。

(128 ビット操作のみ) CR4 の OSFXSR が 0 の場合。

(128 ビット操作のみ) CPUID 機能フラグ SSE2 が 0 の場合。

#NM CRO の TS がセットされた場合。